-

1

-

2

-

3

-

4

-

5

-

6

-

7

-

8

-

9

-

10

-

11

-

12

-

13

-

14

-

15

-

16

-

17

-

18

-

19

-

20

-

21

-

22

-

23

-

24

-

25

-

26

-

27

-

28

-

29

-

30

-

31

-

32

-

33

-

34

-

35

-

36

-

37

-

38

-

39

-

40

-

41

-

42

-

43

-

44

-

45

-

46

-

47

-

48

-

49

-

50

-

51

-

52

-

53

-

54

목차

1.VHDL 의 소개 – 강의 순서

Definition of VHDL

What & Why HDL?

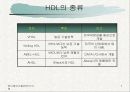

HDL의 종류

VHDL’s History

Benefits of VHDL

Design Automation

디지털 논리회로의 설계환경 변천

Design Flow

2.개발환경의 이해 및 실습 - 강의순서

Design Entry

Project Compilation

Project Simulation

Device Programming

Definition of VHDL

What & Why HDL?

HDL의 종류

VHDL’s History

Benefits of VHDL

Design Automation

디지털 논리회로의 설계환경 변천

Design Flow

2.개발환경의 이해 및 실습 - 강의순서

Design Entry

Project Compilation

Project Simulation

Device Programming

본문내용

Design Automation

컴퓨터 기술의 발달

처리 속도, 저장 용량, GUI의 성능 향상

집적회로 설계 기술의 발달

설계 기술의 축적, 설계 도구의 발달

설계자의 작업 및 결정을 대신하고 검증을 지원.

Definition of VHDL

VHDL is an international IEEE standard specification language for describing digital hardware used by industry worldwide.

VHDL is an acronym for VHSIC( Very High Speed Integrated Circuit) Hardware Description Language.

자세하게 그림,도표로 설명이 되어 있습니다..

컴퓨터 기술의 발달

처리 속도, 저장 용량, GUI의 성능 향상

집적회로 설계 기술의 발달

설계 기술의 축적, 설계 도구의 발달

설계자의 작업 및 결정을 대신하고 검증을 지원.

Definition of VHDL

VHDL is an international IEEE standard specification language for describing digital hardware used by industry worldwide.

VHDL is an acronym for VHSIC( Very High Speed Integrated Circuit) Hardware Description Language.

자세하게 그림,도표로 설명이 되어 있습니다..

추천자료

[논리회로실험] Mux 와 demux 발표 ppt 자료

[논리회로실험] Mux 와 demux 발표 ppt 자료 [논리회로]부울대수의공리

[논리회로]부울대수의공리 7 세그먼트 논리회로 구현

7 세그먼트 논리회로 구현 기본 논리회로 실험

기본 논리회로 실험 숭실대 2-1학기 논리회로실험 예비리포트 모음

숭실대 2-1학기 논리회로실험 예비리포트 모음 TTL게이트와 PLD를 이용한 논리회로 실험 [3장 결과]

TTL게이트와 PLD를 이용한 논리회로 실험 [3장 결과] [논리회로실험] 실험8. 전가산기와 전감산기 예비보고서

[논리회로실험] 실험8. 전가산기와 전감산기 예비보고서 [논리회로실험] 실험11. MUX & DEMUX 예비보고서

[논리회로실험] 실험11. MUX & DEMUX 예비보고서 <전자계산기 일반-논리회로>!!!

<전자계산기 일반-논리회로>!!! [ 대학레포트 ]논리회로 간소화 , BCD 무효코드 검출기에 대한 진리표, 카르노 맵을 이용한 ...

[ 대학레포트 ]논리회로 간소화 , BCD 무효코드 검출기에 대한 진리표, 카르노 맵을 이용한 ... [ 대학레포트 ]논리회로 간소화 - BCD 무효코드검출기에 대한 진리표, 카르노맵을 이용한 표...

[ 대학레포트 ]논리회로 간소화 - BCD 무효코드검출기에 대한 진리표, 카르노맵을 이용한 표... [논리회로설계]ALU 및 Booth 곱셈기

[논리회로설계]ALU 및 Booth 곱셈기 [논리회로설계]ALU를 활용한 shifter 구현

[논리회로설계]ALU를 활용한 shifter 구현 [논리회로설계]FSM binary/gray counter

[논리회로설계]FSM binary/gray counter

소개글