목차

1. 연산증폭기(Operational -Amplifiers)의 구성과 특징

2. 연산증폭기의 동작원리

3. 반전증폭기와 비반전증폭기의회로와 입출력파형

2. 연산증폭기의 동작원리

3. 반전증폭기와 비반전증폭기의회로와 입출력파형

본문내용

연산증폭기의 동작원리와 반전증폭기,비반전증폭기

1-1. 연산증폭기(OP-AMP)의 특징

• 차동 증폭기 • 고이득

• 전압증폭기 ⇒단일 IC내부에서 모두 연결⇒ • 고입력 임피던스

• 출력증폭기 • 저출력 임피던스

〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓

차동증폭기, 전압증폭기, 출력증폭기 회로의 조합으로 구성되는데 이런 3가지 회로들은 고이득, 고입력 임피던스, 저출력 임피던스 증폭기의 기능을 갖도록 단일 IC내부에서 모두 연결된다.

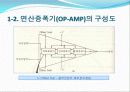

1-2. 연산증폭기(OP-AMP)의 구성

● 연산증폭기는 차동증폭기, 전압증폭기, 출력증폭기 회로의 조합으로 구성된다.

● 두 개의 입력단자와 하나의 출력단자가 있다.

● 두 개의 입력단자 중 하나는 반전입력(Inverting Input)이고 다른 하나는 비반전입력(Non-inverting Input)이다.

1-2. 연산증폭기(OP-AMP)의 구성도

≪ 그 림 ≫

** Offset Null – 출력전압의 제로점조절용

〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓

연산증폭기는 많은 IC들로 구성된 것으로 일반적인 외부 구성도는 그림과 같이 두 개의 입력단자와 하나의 출력단자가 있고 여기 (DC)전원을 공급해 주기 위한 두 개의 단자가 있는데 이는 당연히 있는 것으로 간주되기 때문에 회로에서는 생략한다.

1-1. 연산증폭기(OP-AMP)의 특징

• 차동 증폭기 • 고이득

• 전압증폭기 ⇒단일 IC내부에서 모두 연결⇒ • 고입력 임피던스

• 출력증폭기 • 저출력 임피던스

〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓

차동증폭기, 전압증폭기, 출력증폭기 회로의 조합으로 구성되는데 이런 3가지 회로들은 고이득, 고입력 임피던스, 저출력 임피던스 증폭기의 기능을 갖도록 단일 IC내부에서 모두 연결된다.

1-2. 연산증폭기(OP-AMP)의 구성

● 연산증폭기는 차동증폭기, 전압증폭기, 출력증폭기 회로의 조합으로 구성된다.

● 두 개의 입력단자와 하나의 출력단자가 있다.

● 두 개의 입력단자 중 하나는 반전입력(Inverting Input)이고 다른 하나는 비반전입력(Non-inverting Input)이다.

1-2. 연산증폭기(OP-AMP)의 구성도

≪ 그 림 ≫

** Offset Null – 출력전압의 제로점조절용

〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓〓

연산증폭기는 많은 IC들로 구성된 것으로 일반적인 외부 구성도는 그림과 같이 두 개의 입력단자와 하나의 출력단자가 있고 여기 (DC)전원을 공급해 주기 위한 두 개의 단자가 있는데 이는 당연히 있는 것으로 간주되기 때문에 회로에서는 생략한다.

키워드

추천자료

화학검출기의 종류와 특징

화학검출기의 종류와 특징 에미터 접지 증폭기 예비보고서

에미터 접지 증폭기 예비보고서 (실험 보고서)JFET 공통 소스 증폭기 실험 및 시뮬레이션

(실험 보고서)JFET 공통 소스 증폭기 실험 및 시뮬레이션 JFET 공통 드레인, 게이트 증폭기 실험 및 시뮬레이션

JFET 공통 드레인, 게이트 증폭기 실험 및 시뮬레이션 JFET 및 MOSFET을 이용한 선형증폭기

JFET 및 MOSFET을 이용한 선형증폭기 OP AMP를 이용한 비반전 증폭기 회로 실험 리포트

OP AMP를 이용한 비반전 증폭기 회로 실험 리포트 전자회로실험 설계 대역통과필터

전자회로실험 설계 대역통과필터 가스 크로마토그래프[gas chromatograph]

가스 크로마토그래프[gas chromatograph]  [전자물리실험12] 미분회로 및 적분회로 (예비 + 결과)

[전자물리실험12] 미분회로 및 적분회로 (예비 + 결과) 디지털 신호처리 (Digital Signal Processing)

디지털 신호처리 (Digital Signal Processing) 실험 29. 능동 필터회로 - 목적, 실험장비, 이론 - 저역통과 능동필터, 고역통과 능동 필터, ...

실험 29. 능동 필터회로 - 목적, 실험장비, 이론 - 저역통과 능동필터, 고역통과 능동 필터, ... 11 푸시폴 전력증폭기 실험

11 푸시폴 전력증폭기 실험 [동작원리(작동원리)]LCD, CMOS의 동작원리(작동원리), FED, 제너다이오드의 동작원리(작동원...

[동작원리(작동원리)]LCD, CMOS의 동작원리(작동원리), FED, 제너다이오드의 동작원리(작동원... 결과_A_D변환기와 D_A변환기

결과_A_D변환기와 D_A변환기