목차

1.기판준비

2.보호산화막 증착

3.채널층 불순물 도핑보호산화막 제거

4.건식 산화막형성

5.다결정 실리콩 증착

6.이온주입

7.게이트에칭

8.표면 산화막 식각.

9.소스 드레인영역 플라즈마 도핑

10.RTA

11.금속막 증착

12.전극형성

13.절연층증착

2.보호산화막 증착

3.채널층 불순물 도핑보호산화막 제거

4.건식 산화막형성

5.다결정 실리콩 증착

6.이온주입

7.게이트에칭

8.표면 산화막 식각.

9.소스 드레인영역 플라즈마 도핑

10.RTA

11.금속막 증착

12.전극형성

13.절연층증착

본문내용

소자 제작 공정

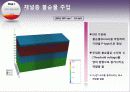

SOI (Silicon-on–Insulator) 기판준비

보호 산화막 (screen oxide) 증착

채널층 불순물 주입

보호 산화막 제거

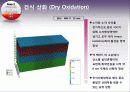

건식산화 (dry oxidation)

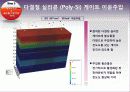

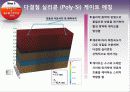

다결정실리콘 (poly-Si) 게이트 증착

다결정실리콘 (poly-Si) 게이트 이온주입

다결정실리콘 (poly-Si) 게이트 식각

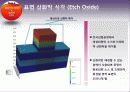

표면 산화막 식각 (etch oxide)

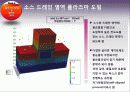

소스 드레인 영역 플라즈마 도핑

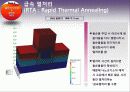

급속 열처리 (RTA)

금속막 증착

전극 형성

절연 보호층 증착

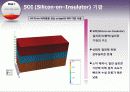

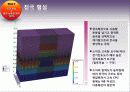

SOI (Silicon-on–Insulator) 기판

SOI(Silicon-on-Insulator)

실리콘/산화막/실리콘

기판의 구조

산화막 절연체 위에 상부실리콘 존재

소자 제작시, 일반 실리콘 기판에 비해 동작 속도가 빠르며 누설 전류가 매우 낮음

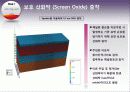

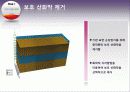

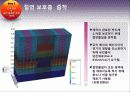

보호 산화막 (Screen Oxide) 증착

채널층 불순물 이온주입 시 발생하는 기판 표면 손상을 방지하기 위해 표면 보호용 산화막 증착

SOI (Silicon-on–Insulator) 기판준비

보호 산화막 (screen oxide) 증착

채널층 불순물 주입

보호 산화막 제거

건식산화 (dry oxidation)

다결정실리콘 (poly-Si) 게이트 증착

다결정실리콘 (poly-Si) 게이트 이온주입

다결정실리콘 (poly-Si) 게이트 식각

표면 산화막 식각 (etch oxide)

소스 드레인 영역 플라즈마 도핑

급속 열처리 (RTA)

금속막 증착

전극 형성

절연 보호층 증착

SOI (Silicon-on–Insulator) 기판

SOI(Silicon-on-Insulator)

실리콘/산화막/실리콘

기판의 구조

산화막 절연체 위에 상부실리콘 존재

소자 제작시, 일반 실리콘 기판에 비해 동작 속도가 빠르며 누설 전류가 매우 낮음

보호 산화막 (Screen Oxide) 증착

채널층 불순물 이온주입 시 발생하는 기판 표면 손상을 방지하기 위해 표면 보호용 산화막 증착

소개글