목차

설계목표 1-3

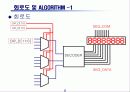

회로도 및 알고리즘 1-2

verilog code and annotation 1-9

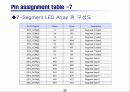

pin assignment table 1-10

simulation result 1-3

실험시 유의사항

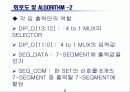

회로도 및 알고리즘 1-2

verilog code and annotation 1-9

pin assignment table 1-10

simulation result 1-3

실험시 유의사항

본문내용

to 1 MUX를 decoding 하여 7-segment로 display.

Part 4에서 사용한 characters인 H.E.L.O를 사용하여 7-segment를 구성

CLK을 주어 하나 decoder 출력을 4개의 7-segment 에 ¼씩 시분할로 할당.

작업 순서

소스 코드 파악 및 예상 출력치 확인

주어진 스펙에 따른 알고리즘 구성

Verilog를 이용한 회로 구성하기

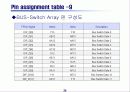

Pin 할당 하기

구현(Implement)하기

트레이닝 키트(COMBO-II) 동작시켜 보기

예상 결과

DIP_D[13:12]의 입력에 2비트의 4개의 값을 스위치로 입력시에 7-segment display에 아래의 값이 출력되어야 한다.

DIP_D[13:12] : 4 to 1 MUX의 SELECTOR

DIP_D[11:0] : 4 to 1 MUX의 입력값

SEG_DATA : 7-SEGMENT에 출력값을 인가

SEG_COM : 한 SET의 신호를 8개의 7-SEGMENT 중 출력될 7-SEGMENT에 할당

module part5(DIP_D,SEG_DATA,SEG_COM,CLK,RESETn);

Part 4에서 사용한 characters인 H.E.L.O를 사용하여 7-segment를 구성

CLK을 주어 하나 decoder 출력을 4개의 7-segment 에 ¼씩 시분할로 할당.

작업 순서

소스 코드 파악 및 예상 출력치 확인

주어진 스펙에 따른 알고리즘 구성

Verilog를 이용한 회로 구성하기

Pin 할당 하기

구현(Implement)하기

트레이닝 키트(COMBO-II) 동작시켜 보기

예상 결과

DIP_D[13:12]의 입력에 2비트의 4개의 값을 스위치로 입력시에 7-segment display에 아래의 값이 출력되어야 한다.

DIP_D[13:12] : 4 to 1 MUX의 SELECTOR

DIP_D[11:0] : 4 to 1 MUX의 입력값

SEG_DATA : 7-SEGMENT에 출력값을 인가

SEG_COM : 한 SET의 신호를 8개의 7-SEGMENT 중 출력될 7-SEGMENT에 할당

module part5(DIP_D,SEG_DATA,SEG_COM,CLK,RESETn);

소개글