목차

가산기

감산기

4진 병렬 가산기 및 가감산기

비교기

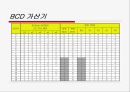

BCD 가산기

감산기

4진 병렬 가산기 및 가감산기

비교기

BCD 가산기

본문내용

반가산기 : 2진수 덧셈에서 두 개의 비트 A와 B를 더한 합 S와 자리올림(carry) C0를 출력하는 조합회로이다.

전가산기 : 두 개의 비트 A, B와 밑자리로부터의 자리올림 C1을 더한 합 S와 윗자리로의 자리올림 C0를 출력하는 조합회로이다.

전가산기 : 두 개의 비트 A, B와 밑자리로부터의 자리올림 C1을 더한 합 S와 윗자리로의 자리올림 C0를 출력하는 조합회로이다.

추천자료

디지털 논리회로

디지털 논리회로 디지털 논리회로 실험 텀프로젝트(디지털 주사위-아주 간단한 카운터회로 이용)

디지털 논리회로 실험 텀프로젝트(디지털 주사위-아주 간단한 카운터회로 이용) 아날로그 및 디지털 회로 설계 실습 - 예비9:래치와 플립플롭

아날로그 및 디지털 회로 설계 실습 - 예비9:래치와 플립플롭 아날로그 및 디지털 회로 설계 실습 - 예비14:패턴인식기 설계

아날로그 및 디지털 회로 설계 실습 - 예비14:패턴인식기 설계 아날로그 및 디지털 회로 설계 실습 - 결과3:Switching Mode Power Supply

아날로그 및 디지털 회로 설계 실습 - 결과3:Switching Mode Power Supply 디지털공학실험 8장 논리회로의간소화(결과)

디지털공학실험 8장 논리회로의간소화(결과) [회로실험] 디지털시계 설계보고서

[회로실험] 디지털시계 설계보고서 디지털 논리와 컴퓨터 설계 4판 솔루션

디지털 논리와 컴퓨터 설계 4판 솔루션 디지털 논리회로

디지털 논리회로 논리회로 : 4 - 3 수치적 연산 - 래치(latch)와 플립플롭(flip-flop) , 레지스터와 카운터

논리회로 : 4 - 3 수치적 연산 - 래치(latch)와 플립플롭(flip-flop) , 레지스터와 카운터  (디지털 실험 보고서) BCD 덧셈기/뺄셈기 구현, Quartus, 조합회로, ALTERA, 논리 게이트

(디지털 실험 보고서) BCD 덧셈기/뺄셈기 구현, Quartus, 조합회로, ALTERA, 논리 게이트 [최신디지털공학실험] 제10판 실험08.논리 회로 간소화 만점레포트 : BCD 무효 코드 검출기 ...

[최신디지털공학실험] 제10판 실험08.논리 회로 간소화 만점레포트 : BCD 무효 코드 검출기 ... [디지털 회로실험] 1장.기본 논리 게이트 (예비)

[디지털 회로실험] 1장.기본 논리 게이트 (예비) 논리회로 설계 과제

논리회로 설계 과제

소개글